Apakah Anda tahu cara mengatasi masalah EMI saat mendesain PCB multi-layer?

Biarkan aku memberitahu Anda!

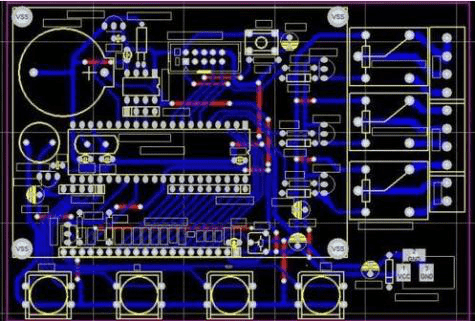

Ada banyak cara untuk mengatasi masalah EMI.Metode supresi EMI modern meliputi: menggunakan lapisan supresi EMI, memilih komponen supresi EMI yang sesuai, dan desain simulasi EMI.Berdasarkan tata letak PCB yang paling dasar, makalah ini membahas fungsi tumpukan PCB dalam mengendalikan radiasi EMI dan keterampilan desain PCB.

bus listrik

Lompatan tegangan keluaran IC dapat dipercepat dengan menempatkan kapasitansi yang sesuai di dekat pin daya IC.Namun, ini bukanlah akhir dari masalah.Karena respons frekuensi kapasitor yang terbatas, kapasitor tidak mungkin menghasilkan daya harmonik yang diperlukan untuk menggerakkan output IC dengan bersih di pita frekuensi penuh.Selain itu, tegangan transien yang terbentuk pada bus daya akan menyebabkan penurunan tegangan pada kedua ujung induktansi jalur decoupling.Tegangan transien ini adalah sumber gangguan EMI mode umum utama.Bagaimana kita bisa memecahkan masalah ini?

Dalam kasus IC di papan sirkuit kami, lapisan daya di sekitar IC dapat dianggap sebagai kapasitor frekuensi tinggi yang baik, yang dapat mengumpulkan energi yang dibocorkan oleh kapasitor diskrit yang menyediakan energi frekuensi tinggi untuk keluaran yang bersih.Selain itu, induktansi lapisan daya yang baik kecil, sehingga sinyal transien yang disintesis oleh induktor juga kecil, sehingga mengurangi EMI mode umum.

Tentu saja, koneksi antara lapisan catu daya dan pin catu daya IC harus sesingkat mungkin, karena tepi naik sinyal digital semakin cepat.Lebih baik menghubungkannya langsung ke pad tempat pin daya IC berada, yang perlu dibahas secara terpisah.

Untuk mengontrol EMI mode umum, lapisan daya harus merupakan sepasang lapisan daya yang dirancang dengan baik untuk membantu memisahkan dan memiliki induktansi yang cukup rendah.Beberapa orang mungkin bertanya, seberapa baik itu?Jawabannya tergantung pada lapisan daya, bahan di antara lapisan, dan frekuensi operasi (yaitu, fungsi waktu naik IC).Secara umum, jarak lapisan daya adalah 6 mil, dan interlayer adalah bahan FR4, sehingga kapasitansi setara per inci persegi lapisan daya sekitar 75pF.Jelas, semakin kecil jarak lapisan, semakin besar kapasitansinya.

Tidak banyak perangkat dengan waktu naik 100-300ps, tetapi menurut tingkat perkembangan IC saat ini, perangkat dengan waktu naik di kisaran 100-300ps akan menempati proporsi yang tinggi.Untuk sirkuit dengan waktu naik 100 hingga 300 PS, jarak lapisan 3 juta tidak lagi berlaku untuk sebagian besar aplikasi.Pada saat itu, perlu mengadopsi teknologi delaminasi dengan jarak antar lapisan kurang dari 1 mil, dan mengganti bahan dielektrik FR4 dengan bahan dengan konstanta dielektrik yang tinggi.Sekarang, keramik dan pot plastik dapat memenuhi persyaratan desain sirkuit waktu naik 100 hingga 300ps.

Meskipun bahan dan metode baru dapat digunakan di masa depan, sirkuit waktu naik 1 hingga 3 ns yang umum, jarak lapisan 3 hingga 6 mil, dan bahan dielektrik FR4 biasanya cukup untuk menangani harmonik kelas atas dan membuat sinyal transien cukup rendah, yaitu , EMI mode umum dapat dikurangi sangat rendah.Dalam makalah ini, contoh desain tumpukan berlapis PCB diberikan, dan jarak lapisan diasumsikan 3 hingga 6 mil.

perisai elektromagnetik

Dari sudut pandang perutean sinyal, strategi pelapisan yang baik adalah menempatkan semua jejak sinyal dalam satu atau lebih lapisan, yang berada di sebelah lapisan daya atau bidang dasar.Untuk catu daya, strategi pelapisan yang baik adalah bahwa lapisan daya berdekatan dengan bidang tanah, dan jarak antara lapisan daya dan bidang tanah harus sekecil mungkin, yang kami sebut strategi "pelapisan".

tumpukan PCB

Strategi penumpukan seperti apa yang dapat membantu melindungi dan menekan EMI?Skema susun berlapis berikut mengasumsikan bahwa arus catu daya mengalir pada satu lapisan dan tegangan tunggal atau beberapa tegangan didistribusikan di berbagai bagian dari lapisan yang sama.Kasus multiple power layer akan dibahas kemudian.

piring 4 lapis

Ada beberapa potensi masalah dalam desain laminasi 4 lapis.Pertama-tama, bahkan jika lapisan sinyal berada di lapisan luar dan bidang daya dan tanah berada di lapisan dalam, jarak antara lapisan daya dan bidang tanah masih terlalu besar.

Jika persyaratan biaya adalah yang pertama, dua alternatif berikut untuk papan 4 lapis tradisional dapat dipertimbangkan.Keduanya dapat meningkatkan kinerja penekan EMI, tetapi keduanya hanya cocok untuk kasus di mana kerapatan komponen pada papan cukup rendah dan terdapat cukup area di sekitar komponen (untuk menempatkan lapisan tembaga yang diperlukan untuk catu daya).

Yang pertama adalah skema yang disukai.Lapisan luar PCB adalah semua lapisan, dan dua lapisan tengah adalah lapisan sinyal / daya.Catu daya pada lapisan sinyal dirutekan dengan jalur lebar, yang membuat impedansi jalur arus catu daya rendah dan impedansi jalur mikrostrip sinyal rendah.Dari perspektif kontrol EMI, ini adalah struktur PCB 4 lapis terbaik yang tersedia.Dalam skema kedua, lapisan luar membawa daya dan ground, dan dua lapisan tengah membawa sinyal.Dibandingkan dengan papan 4 lapis tradisional, peningkatan skema ini lebih kecil, dan impedansi interlayer tidak sebaik papan 4 lapis tradisional.

Jika impedansi kabel harus dikontrol, skema susun di atas harus sangat berhati-hati untuk meletakkan kabel di bawah pulau tembaga catu daya dan pentanahan.Selain itu, pulau tembaga pada catu daya atau lapisan harus saling berhubungan sebanyak mungkin untuk memastikan konektivitas antara DC dan frekuensi rendah.

piring 6 lapis

Jika kerapatan komponen pada papan 4 lapis besar, pelat 6 lapis lebih baik.Namun, efek pelindung dari beberapa skema susun dalam desain papan 6 lapis tidak cukup baik, dan sinyal transien bus daya tidak berkurang.Dua contoh dibahas di bawah ini.

Dalam kasus pertama, catu daya dan arde masing-masing ditempatkan di lapisan kedua dan kelima.Karena impedansi tinggi catu daya berlapis tembaga, sangat tidak menguntungkan untuk mengontrol radiasi EMI mode umum.Namun, dari sudut pandang kontrol impedansi sinyal, metode ini sangat tepat.

Pada contoh kedua, catu daya dan arde masing-masing ditempatkan di lapisan ketiga dan keempat.Desain ini memecahkan masalah impedansi catu daya berlapis tembaga.Karena kinerja pelindung elektromagnetik yang buruk dari lapisan 1 dan lapisan 6, mode diferensial EMI meningkat.Jika jumlah garis sinyal pada dua lapisan luar paling sedikit dan panjang garis sangat pendek (kurang dari 1/20 panjang gelombang harmonik tertinggi dari sinyal), desain dapat memecahkan masalah mode diferensial EMI.Hasil menunjukkan bahwa penekanan mode diferensial EMI sangat baik ketika lapisan luar diisi dengan tembaga dan area berlapis tembaga dibumikan (setiap interval panjang gelombang 1/20).Seperti disebutkan di atas, tembaga harus diletakkan

Waktu posting: Jul-29-2020